PCIe® technology serves as the backbone of data center communication in AI infrastructure. The latest PCIe standards deliver unprecedented data transfer rates—32 GT/s with PCIe 5.0 and 64 GT/s with PCIe 6.0. However, as speeds increase, so do the challenges in maintaining clean, reliable signals over longer distances or complex paths. Higher data rates make signals more susceptible to attenuation, noise, and jitter, leading to potential data corruption or reduced system performance. This makes it critical to employ signal integrity solutions like Retimers and Redrivers.

In simple terms, a Redriver amplifies a signal, whereas a Retimer retransmits a fresh copy of the signal. Retimers are especially important for PCIe 5.0 and 6.0 because they actively recover the signal by retiming and reclocking it, essentially eliminating accumulated jitter and restoring the signal to its original quality. Redrivers, on the other hand, amplify the signal but are less effective at handling jitter.

Understanding these distinctions is crucial as companies scale their AI infrastructure using the latest PCIe technologies.

In this blog, we’ve broken down the key differences between Retimers and Redrivers.

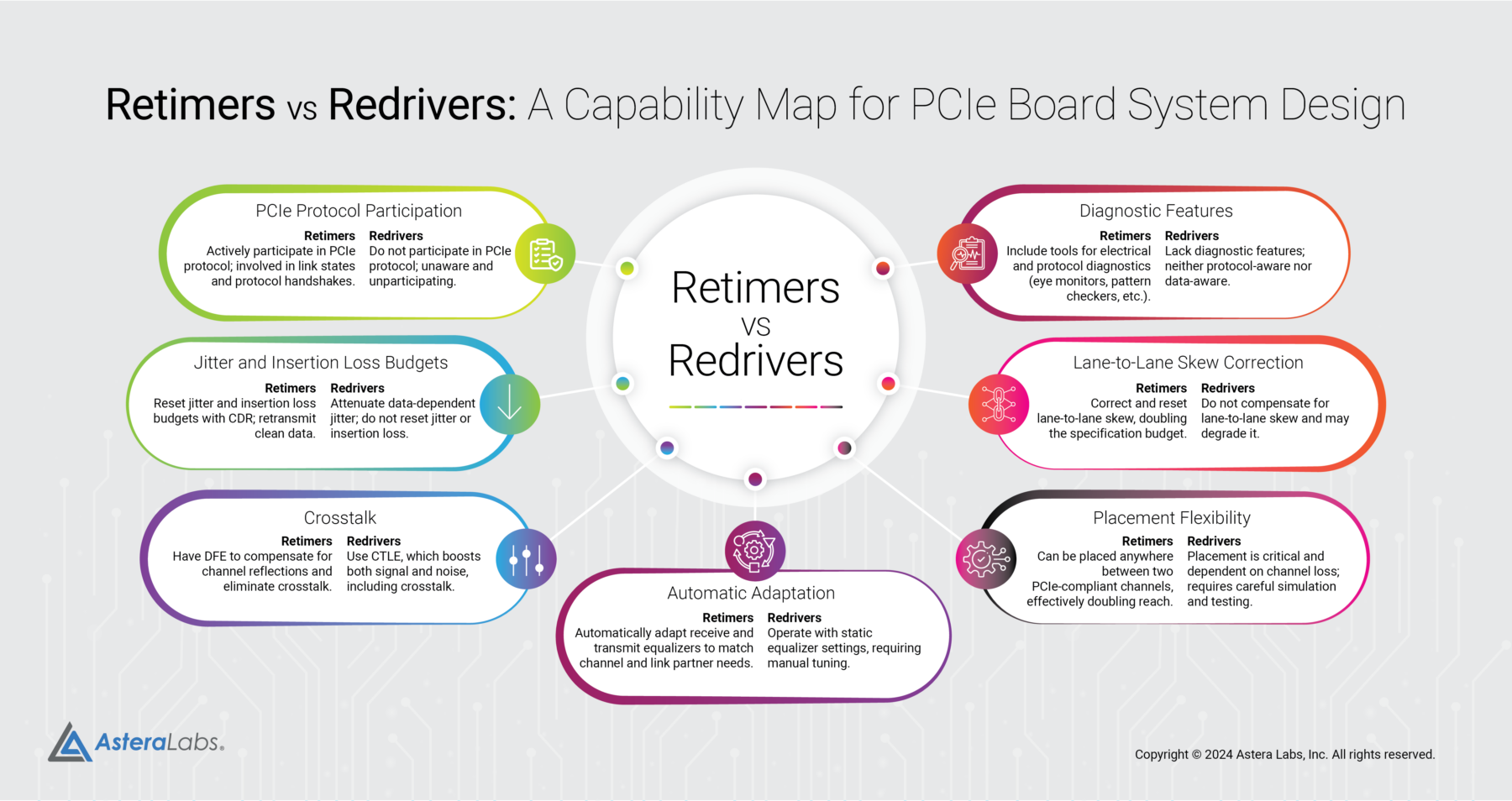

Retimers actively participate in the PCIe protocol; Redrivers do not.

The PCIe base specification spells out how and to what extent Retimers participate in the protocol during Detect, Recovery, L0 and so on. Equalization to the L0 and L1 link states requires value-added functionality from the Retimer (handshakes, timeouts, bit manipulation, etc.). Redrivers are unaware of and unparticipating in the protocol. If the link works reliably the first time, that’s great! But if the link experiences marginality of any sort, it becomes exceedingly difficult to pinpoint whether the problem is physically before the Redriver or after it, since the Redriver’s role in link formation is undefined and unknown to its link partners.

Retimers reset the jitter and insertion loss budgets; Redrivers do not.

A Retimer’s Clock Data Recovery (CDR) fully recovers the data stream and retransmits it on a clean clock. Starting with a fresh copy of the data enables the extension of the channel to twice the original specification. Without a CDR, the best a Redriver can do is attenuate (not reset) the data-dependent jitter (DDJ) caused by intersymbol interference (ISI). A Redriver cannot attenuate uncorrelated or random jitter (RJ). In fact, a Redriver will always add to RJ due to its own device thermal noise in a root-mean-square (RMS) manner.

Retimers reduce and eliminate crosstalk; Redrivers do not.

A Decision Feedback Equalizer (DFE) compensates for reflections in the channel response caused by impedance discontinuities in board vias, connectors and package socket-board interfaces. The nice thing about a DFE is that it is unaffected by crosstalk. The DFE equalizes just as well in the presence of crosstalk, and once the data is sampled by the Retimer’s CDR, crosstalk is eliminated for good. Redrivers use a Continuous Time Linear Equalizer (CTLE) that boosts both the signal and the noise. Crosstalk is not eliminated or even attenuated through a Redriver; in fact, it gets amplified.

Retimers automatically adapt their receive and transmit equalizers to match the characteristics of the channel and the link partner’s needs; Redrivers do not.

A Retimer will examine the signal it receives and adjust the CTLE and DFE to minimize its own bit error rate (BER). Likewise, the Retimer’s transmitter will adjust its de-emphasis and pre-shoot equalization to minimize the link partner’s BER according to PCIe equalization protocol. A Redriver, conversely, operates with a static equalizer setting. The optimal setting (which can be different for every channel in the system) is often painstakingly selected following an exhaustive search in Input/Output Buffer Information Specification (IBIS) algorithmic modeling interface (AMI) simulations and again in lab testing – a process fondly referred to as “tuning.”

Retimers have built-in features to help diagnose link issues (both electrical and protocol); Redrivers do not.

Retimers have tools for assessing the electrical performance (internal eye monitors, pattern generators, pattern checkers) and protocol performance (link state history monitors, timeout adjustments). Redrivers cannot offer such diagnostic features because they are neither protocol-aware nor aware of the actual data passing through. Redrivers do not know what state the link is in.

Retimers correct for lane-to-lane skew; Redrivers do not.

PCIe has a tight requirement on the physical skew between lanes on a board, typically caused by mismatches in channel routing length. Retimers are required to compensate and reset any lane-to-lane skew, effectively doubling the specification budget. Redrivers cannot compensate for lane-to-lane skew, and what’s worse is that they may degrade the skew depending on how symmetric the Redriver package is across all lanes.

Retimers can be placed anywhere between two PCIe-compliant channels; Redrivers cannot.

By definition, Retimers extend the total PCIe channel reach by two times the specification. A Redriver’s reach extension, however, depends on where it is placed in the channel – how much loss is before the Redriver versus how much is after. The specific placement of a Redriver must be carefully determined by IBIS-AMI simulation and experimentation. Too close to the root complex transmitter, and the Redriver’s CTLE will enter nonlinear operation and will have limited benefit. Placed too far from the transmitter, the Redriver’s device noise may significantly degrade the signal-to-noise ratio (SNR) of the data signal. It’s not all bad news for Redrivers. They do have lower power consumption and lower input-to-output latency compared to Retimers. But if the link does not form in the first place or if the BER is too high, none of that matters.

Conclusion

While both Retimers and Redrivers can extend reach of high-speed signals, Retimers offer clear advantages. By fully recovering and reclocking signals, Retimers not only amplify but also correct issues such as jitter and noise that are common at higher PCIe data rates. This makes them the superior solution, particularly in advanced AI environments where performance, reliability, and data accuracy are paramount.

References

Samaan, S., Froelich, D., and Johnson, S. (2015). High-Speed Serial Bus Repeater Primer: Re-driver and Re-timer Micro-Architecture, Properties, and Usage [White paper]. https://www.intel.com/content/dam/www/public/us/en/documents/white-papers/serial-bus-white-paper.pdf

PCI Express Card Electromechanical Specification Revision 4.0 Version 0.9, 2019. https://pcisig.com/